解决方案

SOLUTION

时间: 2023-03-17

浏览量: 1004

BEOL 金属线 RC 延迟已成为限制高级节点芯片性能的主导因素 [1]。更小的金属线间距需要更窄的线 CD 和线间间距,这会引入更高的金属线电阻和线间电容。

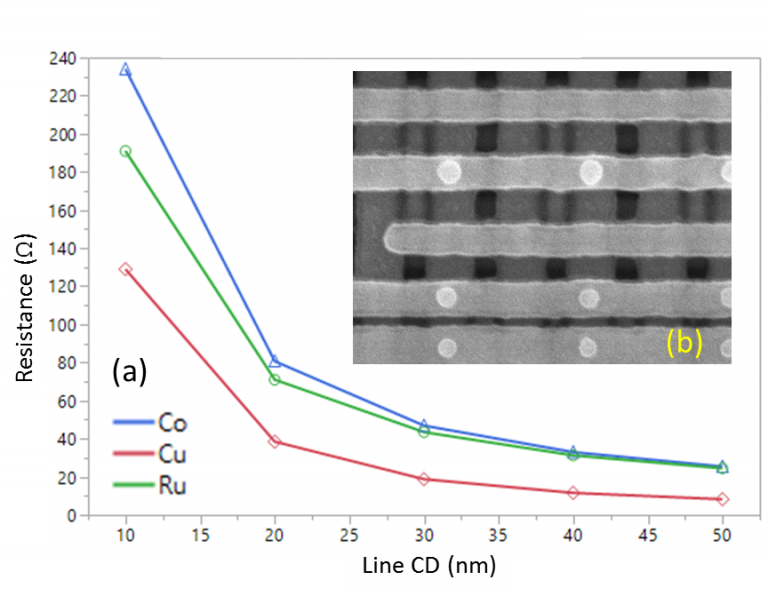

这在图 1 中得到了证明,该图显示了跨不同 BEOL 金属的线路电阻与线路 CD 的模拟。即使没有线边缘粗糙度 (LER),该图也显示电阻随着线宽缩小呈指数增加 [2]。为了缓解这个问题,在更小的节点上需要进行金属线线宽优化和精细的金属材料选择。

线边缘粗糙度也是决定电子表面散射和随后的线电阻率的重要因素。图 1 (b) 显示了具有可见 LER 的典型 5 nm BEOL M2 线的扫描电子显微镜图像 [3]。我们最近使用虚拟过程建模,通过改变 RMS 振幅、相关长度、使用的材料和金属线 CD,研究了 LER 对线电阻的影响。

图 1:(a) 线路电阻与线路 CD,(b) 5 nm M2 的 SEM 顶视图(由 TechInsights 提供)。

在晶圆厂中,通过改变线 CD 和金属来执行 LER 变化实验非常困难、昂贵且耗时。在 Si 晶圆上,由于光刻和蚀刻工艺的可变性和限制,LER 的控制也很困难。在这些情况下,虚拟制造可能是一种更直接、更有效的方式,可以“虚拟”生成实际 LER 金属线结构的复制品,并计算一系列变量的电阻率 [4]。

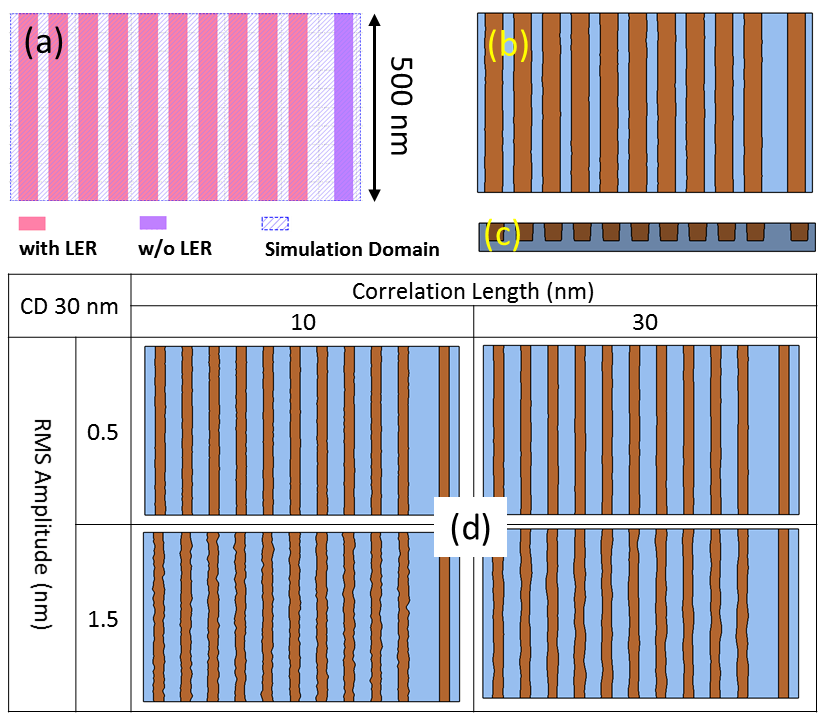

图 2(a) 显示了使用虚拟过程建模平台 (SEMulator3D®) 模拟 LER 的布局设计。图 2(b) 和 2(c) 从顶视图和横截面视图显示了虚拟制造的结构及其模拟的 LER。通过设置特定的 RMS 幅度(噪声幅度)和相关长度(噪声频率)值,可以在虚拟制造的光刻步骤中直接修改 LER。

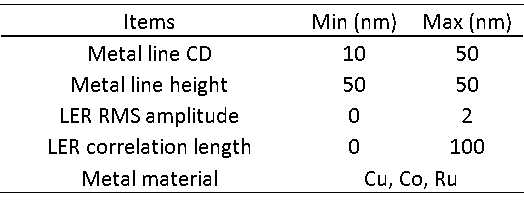

图 2 (d) 显示了不同 LER 条件的简单拆分实验。线边缘粗糙度显示为不同金属线 CD、RMS 振幅和相关长度的函数。此数据是在 SEMulator3D 中的虚拟实验设计 (DOE) 期间生成的。为了系统地研究使用不同 CD 和材料的线边缘粗糙度的影响,使用表 1 所示的拆分条件完成实验拆分。然后从仿真结果中提取相应的金属线电阻。为简单起见,在模拟这些结构时未考虑衬里材料。

图 2:(a) 布局设计,(b) 生成的典型金属线的顶视图,(c) 金属线的横截面图,(d) RMS 的 LER 状态和相关长度拆分。

表 1:DOE 拆分条件。

使用表 1 中的拆分条件完成了 1000 多个虚拟 DOE 实验,以了解 LER 对金属线电阻的影响。在这些实验中,我们了解到:

LER 控制在高级节点将变得越来越重要,因为 LER 对较小金属线 CD 的电阻有很大影响。我们在工艺建模拆分实验期间通过改变金属线 CD 和金属线材料来研究 LER 对金属线电阻的影响。

在 EUV 光刻期间,CDU 和 LER 可能会出现问题,因为大多数 EUV 工具的测试成本高且能量密度低。在这些情况下,可能需要修改光刻开发以最大限度地减少 LER。这些修改可以进行虚拟测试,以降低开发成本。新的 EUV 抗蚀剂方法(例如 Lam Research® 提出的干法抗蚀剂)也可能有助于在较低的 EUV 曝光能量下降低线边缘粗糙度。

在高级节点,需要正确选择金属线材料,CD优化和抵抗开发,以减少由电子表面散射引起的LER和线电阻。未来节点可能还需要额外的 LER 改进(光刻后),以减少 LER 引起的电阻。

Chen, H. C., Fan, S. C., Lin, J. H., Cheng, Y. L., Jeng, S. P., & Wu, C. M. (2004). The impact of scaling on metal thickness for advanced back end of line interconnects. Thin solid films, 469, 487-490.

van der Veen, M. H., Heyler, N., Pedreira, O. V., Ciofi, I., Decoster, S., Gonzalez, V. V., … & Tőkei, Z. (2018, June). Damascene benchmark of Ru, Co and Cu in scaled dimensions. In 2018 IEEE International Interconnect Technology Conference (IITC) (pp. 172-174). IEEE.

Techinsights TSMC 5nm logic tear down report.

http://www.coventor.com/products/semulator3d

联系我们