解决方案

SOLUTION

时间: 2023-04-02

浏览量: 1128

Coventor 提供用于发明下一代智能电子产品的高度先进的过程建模和设计自动化解决方案。我们致力于帮助客户取得成功,解决半导体和 MEMS 行业的实际工艺开发、设计和集成问题。Coventor 正在帮助建立一个电子设备的互联世界,这将提高全球的生产力和生活质量。

铜(Cu)的电阻率取决于其晶体结构、孔隙体积、晶界和材料界面失配,这在较小尺度下变得更加显著。铜线的形成传统上是通过使用沟槽蚀刻工艺在低介电常数二氧化硅中蚀刻沟槽图案,然后通过镶嵌流程用铜填充沟槽来完成的。不幸的是,这种方法会产生具有明显晶界和孔隙的多晶结构,这会增加铜线电阻。在这个过程中还会使用高电阻的TaN衬底材料,以防止镶嵌退火过程中的铜扩散。

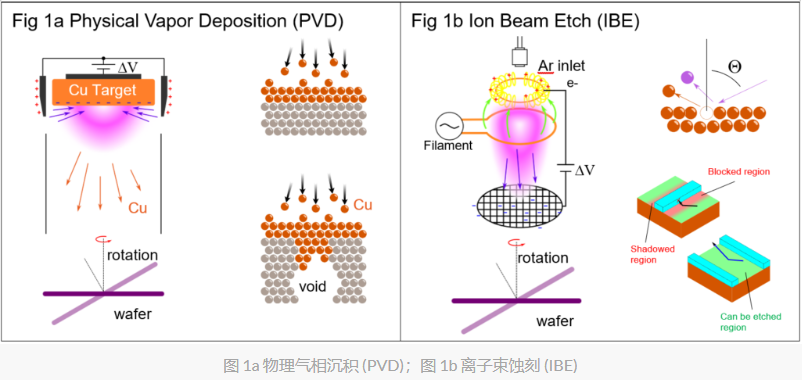

物理气相沉积(PVD)可以在高动能(10至100电子伏特之间)下沉积铜,形成低电阻、致密的单晶结构。然而,PVD 沉积有着直线传输限制,只能在平坦表面上均匀地沉积。因此,它不能用于填充深孔或槽(图1a)。要形成孤立的导线形状,必须在平坦表面上沉积均匀的铜层,然后通过离子束物理刻蚀来形成形状。由于铜不会与反应性气体形成挥发性化合物,因此无法使用反应离子刻蚀过程。

在离子束刻蚀(IBE)过程中产生的加速的氩离子,如果入射角非常大,则可以去除铜。不幸的是,由于掩模遮挡效应,可刻蚀区域将受到限制(图1b中红色区域)。这种刻蚀失败是由于阴影效应或射出原子的路径被阻挡造成的。当掩膜与离子束的路径平行时,所有未被掩膜遮挡的区域均可被刻蚀。因此,离子束刻蚀仅限于刻蚀任意长度的线形掩模。

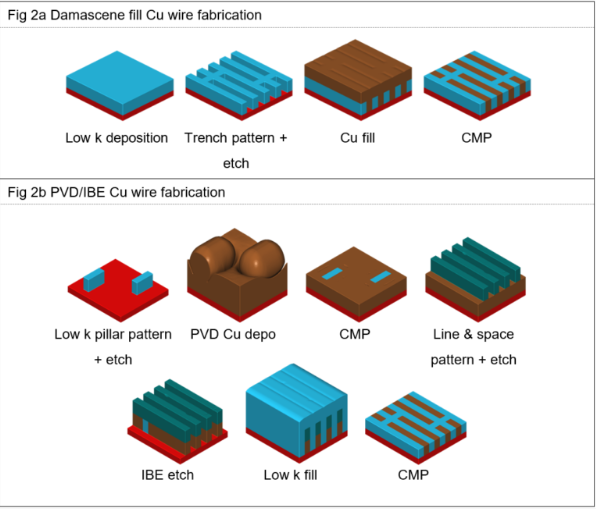

为了了解沉积和刻蚀对线路电阻的影响,我们使用 SEMulator3D® 能见度沉积和刻蚀函数对 PVD 和 IBE 刻蚀过程进行建模。在 SEMulator3D 中,使用了 30 度角度分布的能见度沉积过程来模拟 AR 离子轰击时铜原子的随机性喷射。模型中使用了 2 度角度分布和 60 度极角倾斜的能见度刻蚀来模拟具有低束流发散度的网格加速离子的行为,假定两个晶圆均具有自由旋转。为了满足 IBE 和 PVD 的限制,并创建所需的最终结构的等效形状,还包括了其他工艺步骤。图2显示了使用铜钨化填充(图2a)和 PVD/IBE工艺(图2b)创建的相同结构。

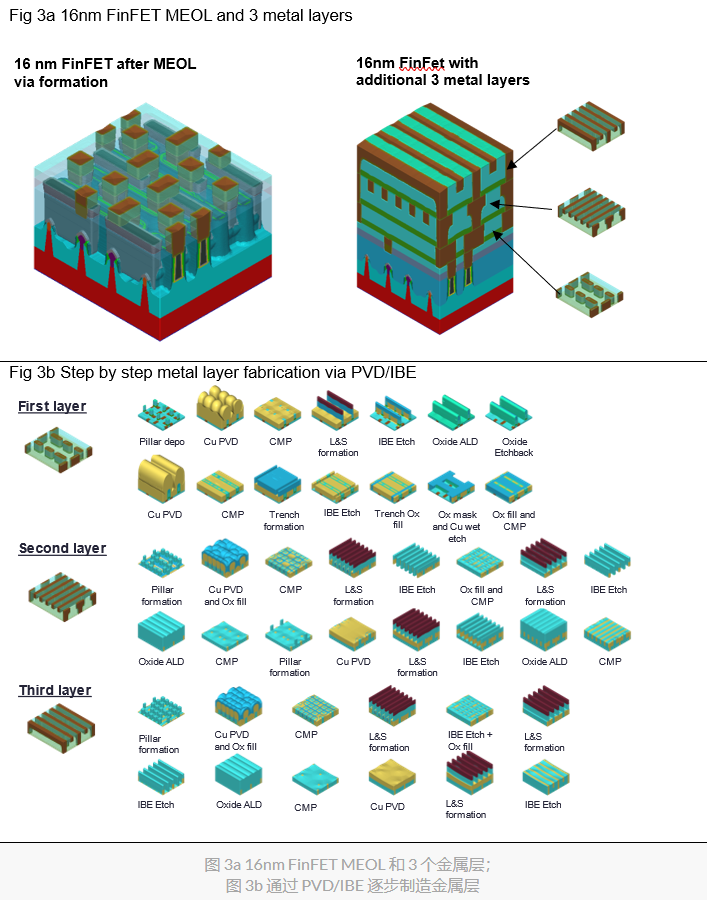

我们展示了一种等效的16纳米静态随机存取存储器(SRAM)电路单元,可以采用物理气相沉积(PVD)/离子束雕刻(IBE)技术制造,并遵守这些限制。由于中线末端以上的所有金属层都是从平坦表面制造的,这使得它成为PVD/IBE线路的理想候选,而不像FinFET器件中所见的复杂互连拓扑结构。图3展示了每个金属层的孤立结构,以及使用PVD/IBE创建三个金属层FinFET结构所需的必要步骤。

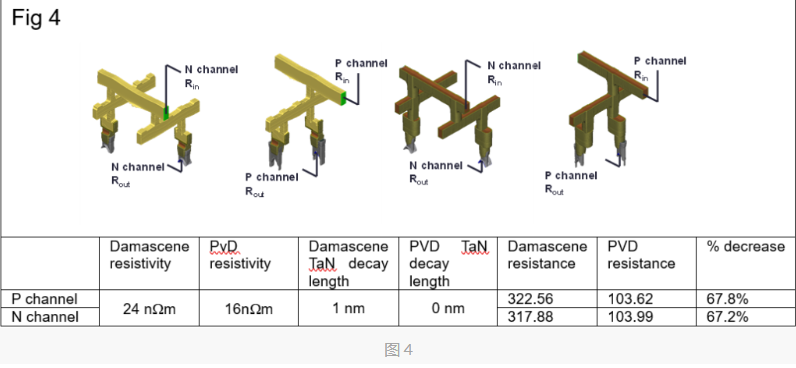

我们对FinFET P和N通道的金属层至过渡层的电线电阻进行了测量,分别使用了铜坑填充(Damascene流程)和物理气相沉积(PVD)两种工艺。图4展示了P和N通道电阻测量的起点和终点(其他绝缘材料为透明)。

为了补偿TaN衬底和铜线之间的界面电阻,我们将铜的电阻率增加了一个指数衰减常数,该常数是以距离TaN界面最近的距离为函数的1纳米。由于铜坑填充工艺不会完全结晶,因此我们将铜的电阻率增加了50%。PVD/IBE铜工艺不使用TaN衬底,因此没有应用指数衰减函数,这个模型中使用了铜的体电阻率。图4中包括了比较Damascene流程和PVD的电阻率的表格。

据我们的模型计算出的电阻值表明,与传统的沟槽蚀刻后进行镶嵌沉积相比,我们可以使用 IBE/PVD 制造方法将电阻降低 67%。发生这种情况是因为在 IBE/PVD 中不需要 TaN 衬里,并且在此过程中 CU 电阻率较低。与金属线形成过程中的镶嵌填充相比,使用 IBE/PVD 可以提高电阻率,但代价是制造工艺更复杂。

联系我们