解决方案

SOLUTION

时间: 2023-04-10

浏览量: 1354

许多存储器和逻辑器件的半导体加工过程中需要 CMP(化学机械平面化)。CMP 用于在半导体制造过程中创建平面并实现均匀的层厚度,并在下一个处理步骤之前优化器件拓扑。

遗憾的是,CMP 后半导体器件的表面并不均匀,这是因为在此过程中去除率不同。平面化过程中的 CMP 浆料、压力、磨料和其他 CMP 变量等因素会导致表面去除率不均匀。CMP 去除率的这些变化会导致凹陷和侵蚀缺陷。CMP 可以在具有不同布局密度的图案化晶圆中创建多样化和意想不到的拓扑结构,不仅在局部而且在整个晶圆上都是如此。

在存储器和逻辑器件的所有 CMP 工艺中,BEOL(后端生产线)半导体工艺中的金属 CMP 变得越来越重要。由于图案密度差异导致的 CMP 腐蚀和凹陷缺陷正在成为一个重要问题,因为金属线间距和宽度正在减小。这些凹陷和侵蚀缺陷会导致 BEOL 结构中的良率损失和可靠性问题 [1]。

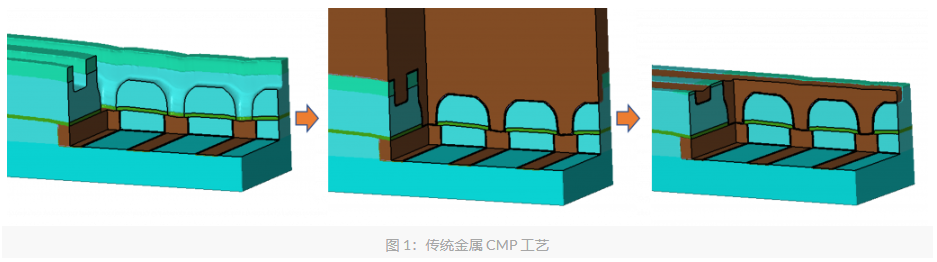

图 1 示意性地说明了半导体器件的 BEOL 部分中的传统金属 CMP 工艺。介电蚀刻步骤后,金属沉积在器件上。蚀刻步骤使用镶嵌工艺来形成 M2 和 Via。之后,发生化学机械平面化。在 CMP 工艺中,主要金属以高去除率进行抛光,直到露出阻挡层金属。接下来,去除阻挡金属直至介电层。最后,在过度抛光步骤中,抛光金属和介电层以去除晶圆上残留的任何金属残留物。

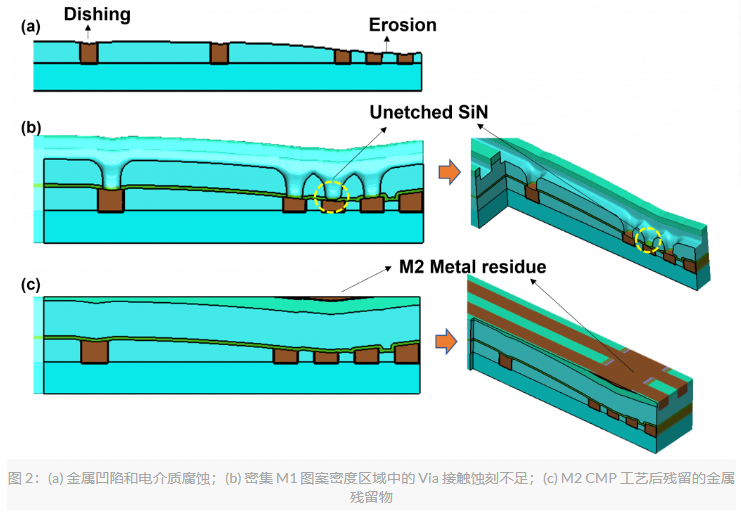

不幸的是,在过度抛光过程中,可能会发生侵蚀和凹陷。电介质腐蚀会受到金属图案密度的影响,凹陷会受到图案/沟槽宽度的影响 [2]。

图 2(a) 显示了 CMP 后腐蚀和凹陷的示例。在图表右侧的密集图案区域可以看到侵蚀,而左侧则显示凹陷。这种电介质腐蚀和凹陷会导致通孔接触问题。在图 2(b) 中,SiN 块在电介质蚀刻步骤中未完全蚀刻,蚀刻过程在通孔到达 M1 金属层之前停止,这是由于器件致密 M1 部分中的中间 SiN 层(右图) )。

这种不完整的蚀刻工艺会在 M1 和通孔之间产生高电阻 (HR) 缺陷,从而导致 RC 延迟和性能问题。

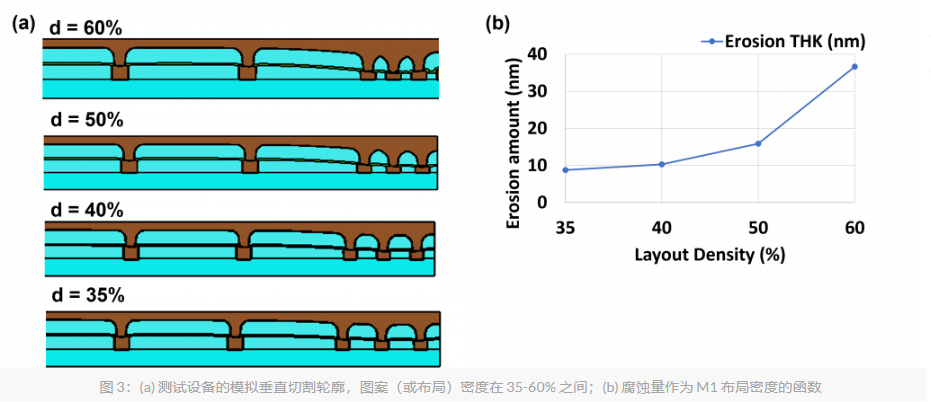

工程师可以使用 SEMulator3D® 工艺模拟来分析 CMP 缺陷,包括图案密度变化引起的侵蚀和凹陷。CMP 工艺模型可以使用实际晶圆数据进行校准,随后在 SEMulator3D 中以不同的图案密度进行模拟。

在图 3 中,CMP 仿真模型的结果显示了具有相同线宽设计的不同布局密度。侵蚀量随布局密度变化的图表表明,模拟中侵蚀厚度随着布局密度的增加而增加。

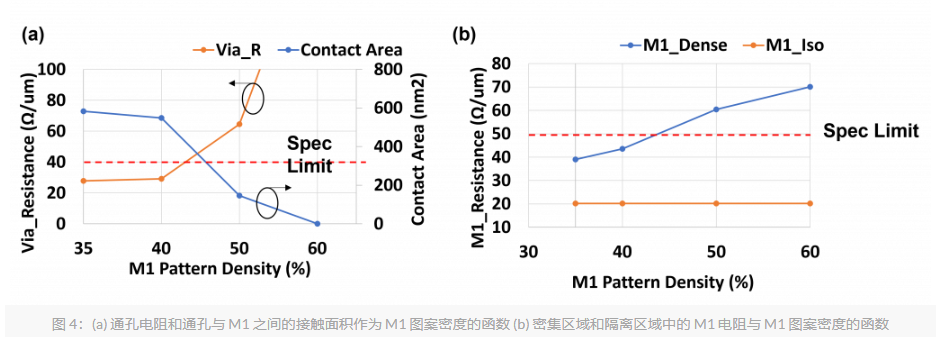

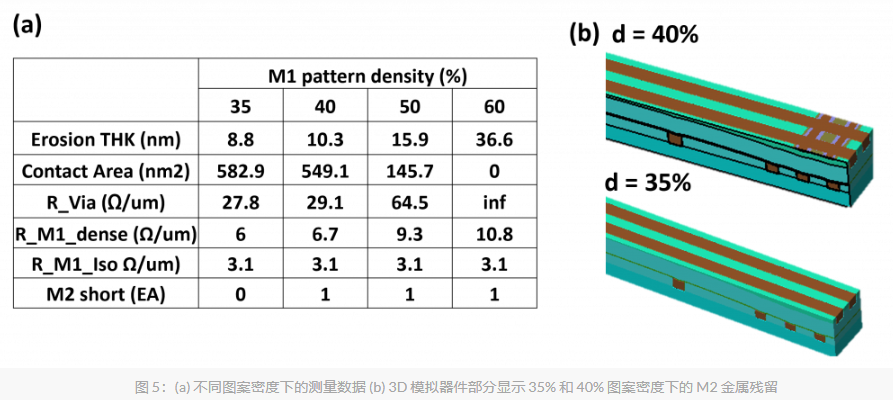

不幸的是,如果仅基于与 M1 和 Via 电阻相关的数据,选择 40% 的最大图案密度可能是一个错误的决定。M2 CMP工艺完成后也可能存在金属残留缺陷,图案密度会影响CMP后金属残留量和后续缺陷(如前所述)。

在图 5a 中,当图案密度从 35% 增加到 40% 时,金属残留缺陷(M2 线上的电短路)变得明显。在 SEMulator3D 中,通过提取电阻或计算单独(未短路)M2 金属线的数量来测量短路缺陷。在这个例子中,我们查看了非短路金属线的数量以检查是否存在短路缺陷。模拟表明在 35% 的图案密度下没有短路,但由于 M2 金属残留缺陷,当图案密度为 40% 或更大时,短路的数量从 0 增加到 1(图 5b)。

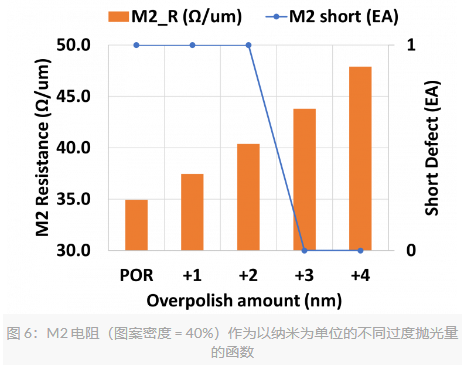

可以增加 CMP 过度抛光步骤以在 M2 CMP 工艺期间去除额外的 M2 金属残留物,但它也会降低 M2 高度并增加 M2 电阻。如图 6 所示,可以使用额外的 3 纳米过度抛光(与记录工艺相比)以 40% 的图案密度去除第二个预测的短路缺陷。不幸的是,这种额外的 3 nm CMP 过度抛光会产生不可接受的 M2 电阻(超过 40 欧姆/um 预算),因此不建议这样做。但也会降低M2的高度,增加M2的电阻。

如图 6 所示,可以使用额外的 3 纳米过度抛光(与记录工艺相比)以 40% 的图案密度去除第二个预测的短路缺陷。不幸的是,这种额外的 3 nm CMP 过度抛光会产生不可接受的 M2 电阻(超过 40 欧姆/um 预算),因此不建议这样做。但也会降低M2的高度,增加M2的电阻。如图 6 所示,可以使用额外的 3 纳米过度抛光(与记录工艺相比)以 40% 的图案密度去除第二个预测的短路缺陷。

不幸的是,这种额外的 3 nm CMP 过度抛光会产生不可接受的 M2 电阻(超过 40 欧姆/um 预算),因此不建议这样做。

在这种情况下,当我们考虑与 CMP 腐蚀、凹陷、电阻和当前 CMP 工艺能力相关的所有模拟数据时,正确的设计决策是将图案密度限制在 35%。基于这项研究,可以通过优化设计规则来限制局部金属图案密度,并通过实施 CMP 工艺改进来减少高图案密度区域的金属腐蚀,从而提高 BEOL 产量和可靠性。

联系我们