解决方案

SOLUTION

时间: 2023-06-12

浏览量: 813

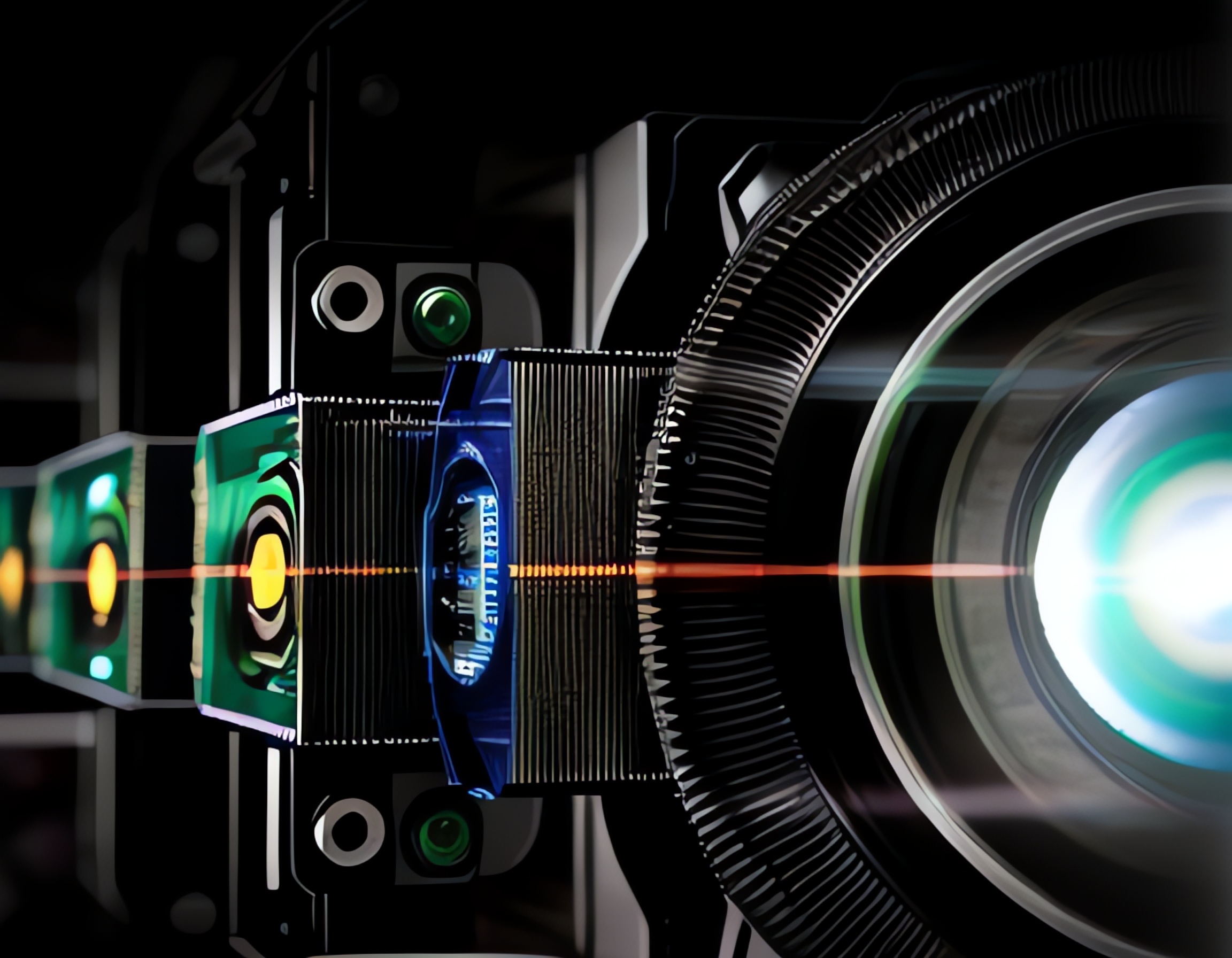

随着晶体管尺寸的缩小,短沟道效应使晶体管栅极更难打开和关闭晶体管 [1]。克服这个问题的一种方法是从平面晶体管架构转向3D设备。全环栅 (GAA) 架构是此类3D设备的一个示例 [2]。

在GAA晶体管中,栅极氧化物在所有方向上都围绕着沟道。GAA晶体管制造过程中的一个关键过程涉及通道释放步骤。该工艺步骤用于蚀刻掉SiGe纳米片之间已沉积的SiGe[3]。理想的蚀刻工艺将去除所有SiGe而不会去除任何硅。

然而,在实践中,工艺工程师在留下一些残留的SiGe和过度蚀刻周围的硅之间进行权衡。去除所有残留SiGe的侵蚀性蚀刻工艺会导致不利的硅损失。另一方面,试图最大限度地减少硅损失可能导致蚀刻通道释放步骤后仍留下SiGe,导致器件性能不佳。

使用半导体工艺模拟和虚拟工艺窗口探索,可以更好地理解残留 SiGe、过蚀刻硅和沟道宽度之间的权衡。使用这种技术,可以完成改变蚀刻时间、蚀刻横向比、蚀刻选择性(在SiGe和Si之间)和通道宽度的虚拟实验设计,以确定GAA通道释放过程中的一组最佳权衡。通过测量(虚拟地)纳米片内硅和SiGe之间的接触面积来表征SiGe残留(同时忽略外延生长的源漏SiGe)。

本文中描述的实验虚拟设计是使用Coventor旗下的软件运行完成的,使用用于创建器件有源区的光刻步骤的 y 偏置改变通道宽度。蚀刻横向比、蚀刻选择性和蚀刻时间也随着DOE参数而变化。

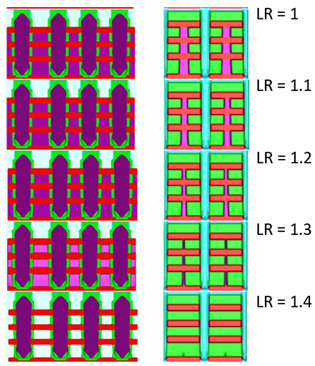

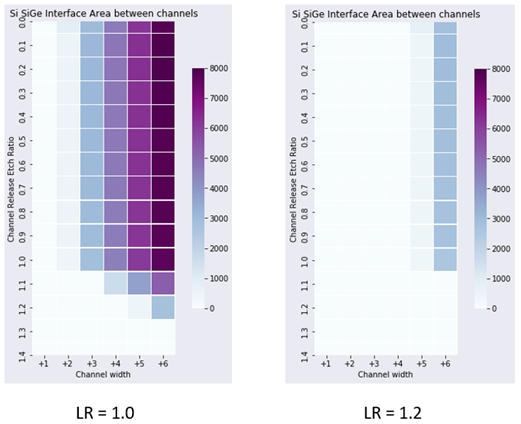

GAA FET的虚拟模型,显示通道释放步骤后残留的SiGe。工艺工程师必须在硅损失和残余SiGe之间做出权衡。(b) 残余SiGe的变化作为沟道宽度和蚀刻横向比的函数。沟道宽度越大,蚀刻掉所有SiGe所需的横向比就越高。通道宽度显示为标称值30nm的增量值

如上所示,SiGe存在于Si纳米片之间,需要在横向方向进行SiGe蚀刻。大通道宽度会干扰这种横向蚀刻工艺。避免残留SiGe对沟道宽度设置了上限,这反过来又限制了器件的载流能力。

在我们的虚拟实验中,我们将通道宽度从其标称值30nm增加,以确定更大通道宽度的影响。上图显示了残留SiGe随沟道宽度和横向蚀刻比的变化。正如预期的那样,更大的沟道宽度需要更高的横向蚀刻比才能完全蚀刻掉SiGe。如果横向比不够高,一些 SiGe 会保留在 Si 纳米片之间。

GAA FET虚拟模型的横截面视图。该图显示了当横向比从1到1.4变化时对残余SiGe的影响,同时沟道宽度从30nm的标称值增加到42nm的值。与上一图的情况相比,在右侧的侧视图中可以看出,需要更高的横向比才能完全蚀刻纳米片之间的所有SiGe

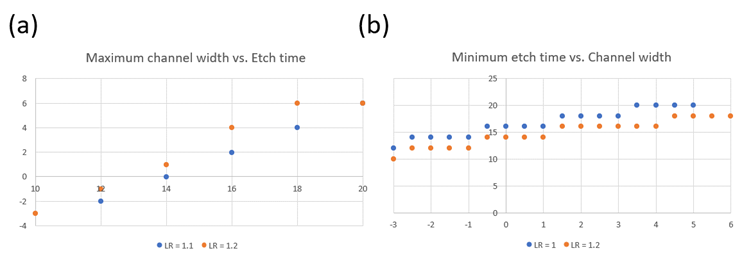

上图显示了使用具有较大沟道宽度(标称+6nm)的器件改变蚀刻横向比对残留SiGe量的结果。随着沟道宽度的增加,完全蚀刻所有SiGe所需的横向比增加。在下图中,我们强调了沟道宽度与蚀刻掉所有SiGe所需的蚀刻时间之间的关系。随着我们增加蚀刻时间,可以增加最大沟道宽度而不会留下任何残留的SiGe(下图a)。随着沟道宽度的增加,蚀刻所有SiGe所需的最短蚀刻时间也如预期的那样增加(下图b)。

(a) 随着我们增加蚀刻时间,在没有任何残留SiGe的情况下可以支持的最大沟道宽度增加。(b) 随着沟道宽度的增加,蚀刻所有SiGe的最小蚀刻时间也增加。通道宽度显示为标称值30nm的增量。

在目前的结果中,我们假设在Si和SiGe之间存在无限的蚀刻选择性。下一步,我们将蚀刻选择性引入我们的实验中。我们改变了Si和SiGe之间的蚀刻选择性,并研究了这些变化对通道释放过程的影响(下图)。为了支持更高的通道宽度,我们发现我们需要增加蚀刻选择性或蚀刻工艺的横向比。

对于两种不同的蚀刻横向比,残留SiGe随蚀刻选择性和沟道宽度的变化。较高的横向比会蚀刻更多的SiGe,并且对于任何给定的蚀刻选择性都允许更大的沟道宽度。通道宽度显示为标称值30nm的增量。

从这些图中,我们可以推导出为我们的GAA器件实现目标器件特性(和性能)所需的工艺窗口。例如,横向比为1,蚀刻时间为20秒,沟道宽度需要在37至40nm范围内,以实现零残留SiGe和最佳器件性能。

结论

执行虚拟实验设计以研究GAA晶体管沟道释放过程中残留SiGe、蚀刻比、蚀刻选择性和沟道宽度之间的关系。这种类型的虚拟工艺窗口探索可用于在开发高级GAA晶体管架构期间快速优化工艺参数,而无需进行昂贵且耗时的基于晶圆的实验。

联系我们