解决方案

SOLUTION

时间: 2023-08-31

浏览量: 1205

线边缘粗糙度(LER)可能发生在光刻的曝光步骤[1-2]中。类似地,蚀刻和沉积工艺步骤可以在半导体表面上留下粗糙度。LER是一个随机(或随机)过程,它可能导致器件缺陷并导致器件性能的变化。这种影响在超过5nm的先进技术节点中更为明显,因为随着器件尺寸的缩小,对这些类型的变化的容忍度较小。过程窗口优化研究可以帮助集成工程师研究LER并制定过程规范,以实现其目标产量。这些类型的过程窗口优化研究可以使用SEMulator3D®过程建模进行自动化和加速。

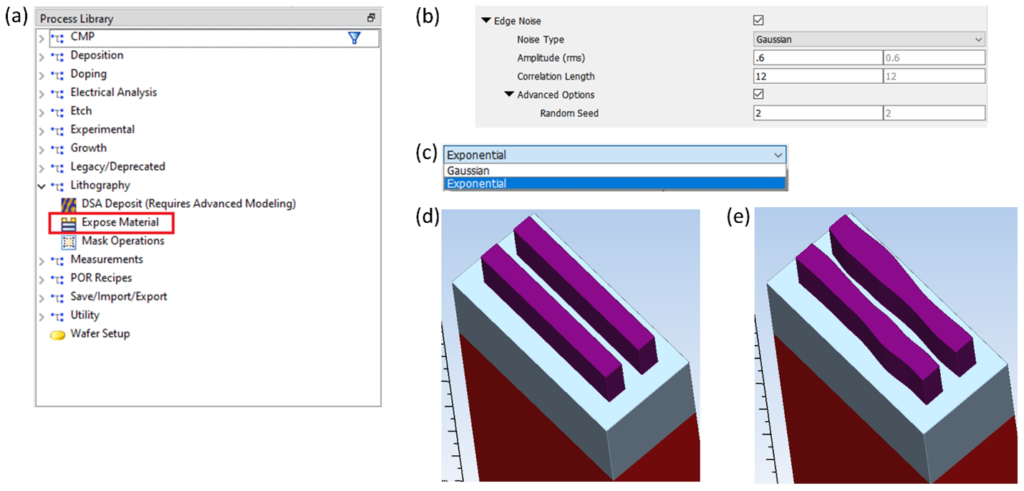

图1(a-c)说明了如何使用SEMulator3D®将LER纳入过程建模。LER可以在SEMulator3D中使用“暴露材料”步骤中的“边缘噪声”选项进行建模(这是光刻工艺库的一部分)。如果模型中不包括LER,则图案化的线将是直的,没有任何粗糙度[图1(d)]。在典型的工艺流程中,这些直边是不现实的。具有边缘粗糙度的典型图案化线的更具代表性的情况如图1(e)所示,其中边缘噪声包含在模型中。

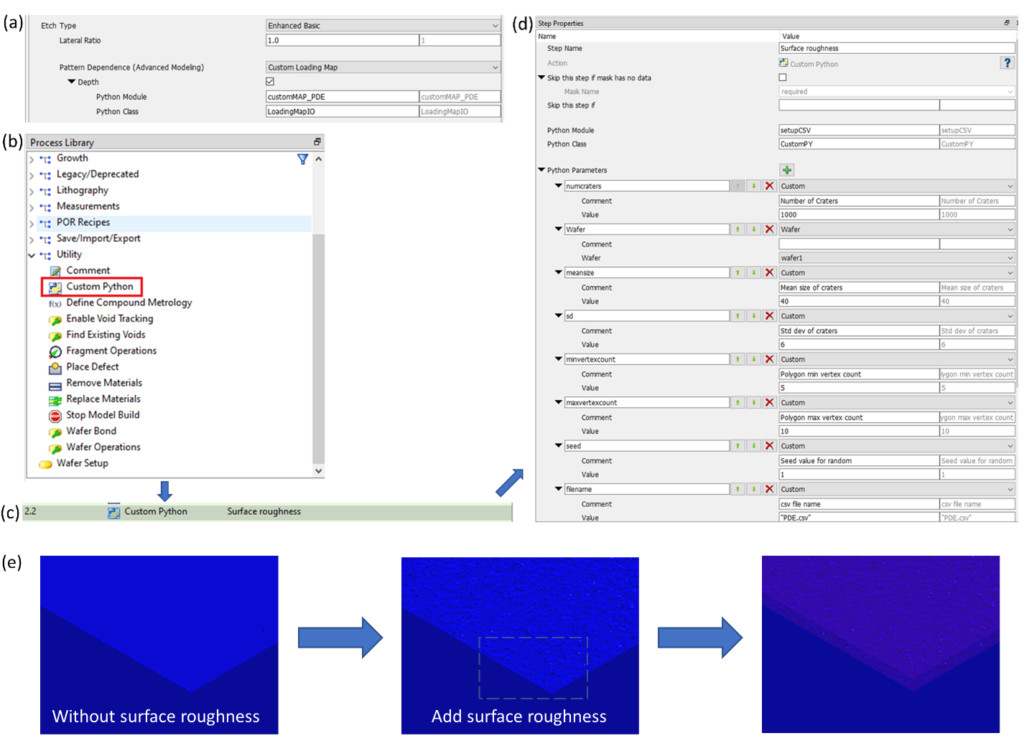

接下来,我们将演示如何模拟表面粗糙度。我们首先使用Process Library中的蚀刻步骤,然后在Pattern Dependency模型中选择“Custom Loading Map”选项[图2(a)]。当选择“深度”选项时,它允许用户指定Python模块和类来确定蚀刻深度。此类选项需要有一个相关的阵列,并且该阵列中的值控制表面上每个点的蚀刻深度。[图2(b-d)]。自定义Python步骤可以包括用于控制形成的表面粗糙度类型的条目。这些条目包括粗糙度特征“计数”,以及构成表面粗糙度的表面凹坑的平均值和标准偏差。陨石坑是多边形的,这些多边形的顶点数量也可以由这些条目控制。

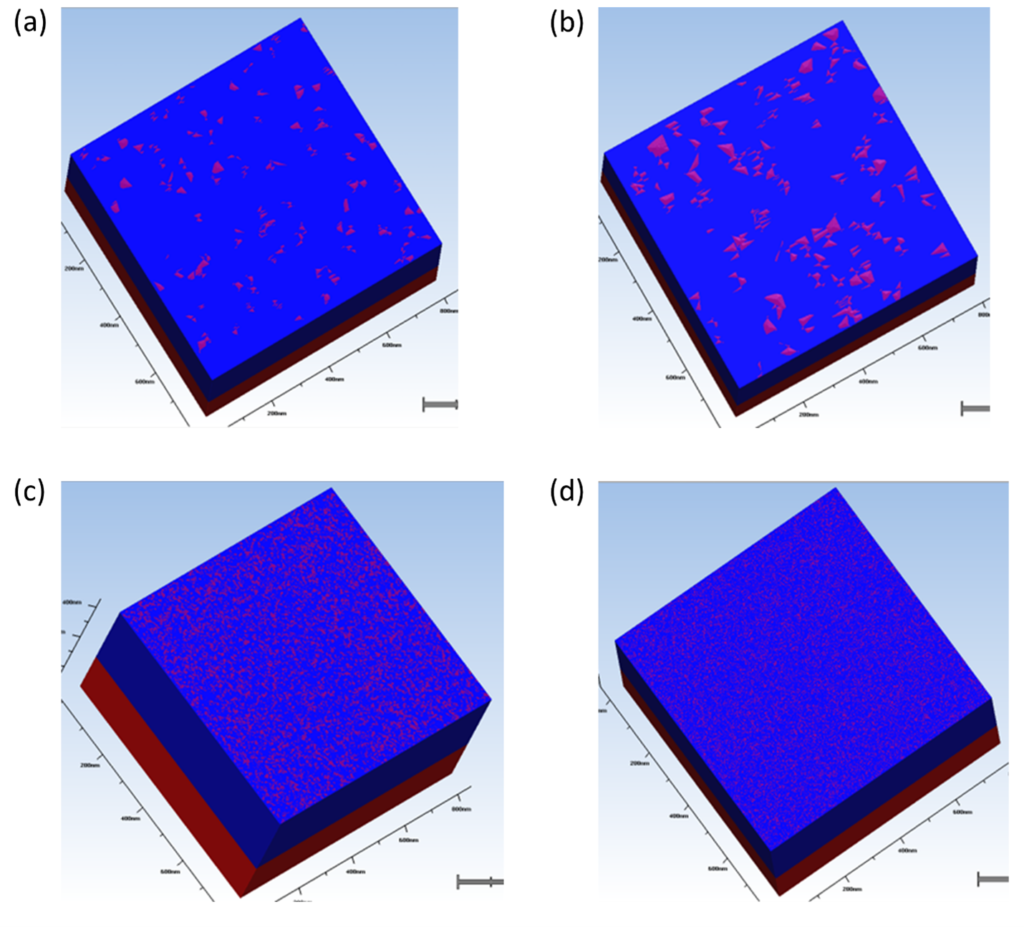

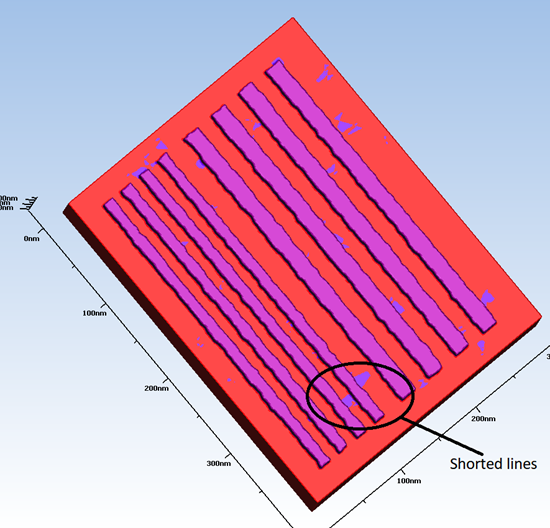

该工艺步骤产生的表面粗糙度将根据提供给模型的参数值而变化。图3(a)显示了二氧化硅表面蚀刻步骤中产生的平均尺寸为40 nm的粗糙度。可以选择参数值来改善模型和实际晶圆结果之间的相关性[图3(a-d)]。表面粗糙度通常会转移到后来蚀刻或沉积的材料上。例如,表面粗糙度会导致光刻胶中的浮渣[3],进而导致线条之间的短路(图4)。

结论:

随着半导体器件尺寸的减小,可以使用LER的虚拟建模和校准来最小化LER的影响。SEMulator3D中的过程窗口优化研究可以包括LER效应,以提高模型精度并最终对测量结果进行校准。使用LER的过程窗口优化建模可以显著提高高级节点预测产量和实际测量产量之间的相关性,这些影响的敏感性最为显著。SEMulator3D®能够准确地对线路和表面粗糙度问题进行建模,以帮助工程师更好地理解和控制先进设备制造过程中LER的后果。