解决方案

SOLUTION

时间: 2023-09-13

浏览量: 835

简介:

逻辑器件(如FinFETs)中,金属栅寄生电容会对电气性能产生负面影响。减少这种寄生电容的一种方法是优化金属栅槽深度。然而,如果仅仅移除更多的金属材料,减少这种电容的程度将受到限制,因为这可能通过改变金属栅槽的形状而意外地改变电容。改变金属栅凹槽的配置,使用尖头或天线形状的配置,有可能有助于平衡电阻和电容值,并提高电气性能。我们现在将回顾使用 SEMulator3D® 虚拟设计实验 (DOEs) 来预测在不同栅关键尺寸 (CDs)、金属栅凹槽深度和金属栅凹槽配置下的电阻和电容的结果。

方法学:

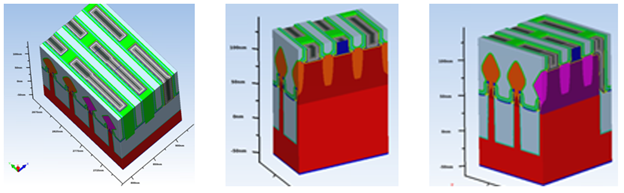

为了这项研究,使用SEMulator3D组装了一个5纳米FinFET工艺流程。POR间距为44纳米(见图1,最左侧)。门电极CD设定为20纳米,沟槽CD设定为24纳米。为了在不同几何形状下提供适当的电阻值,针对TiN、TiAl和W金属衬底建立了特定的材料属性用于尺寸校正。SAC(自对准接触)Cap氮化物CMP(化学机械抛光)步骤在达到特定的氧化物后,保持在30nm的恒定过抛深度。作为我们金属栅凹陷剖面研究的一部分,我们改变了栅CD和W刻蚀退回步骤。为了改变栅CD,X方向上的尺寸偏差每侧修改1nm。门极电容的尺寸从6纳米到30纳米,增量为2纳米。对于蚀刻后的W(氧化物)退避(W ETB)步骤,增量范围从25纳米到60纳米,增量为5纳米。

为了测量电阻,我们在我们的工艺模型中建立了电阻端口。我们使用切割平面法在NFET epi和PFET epi之间建立了一个端口(见图1,中间和右侧较远位置)。然后我们测量了金属栅之间的电阻。除了这些电阻计算之外,我们还计算了带有尺寸修正和不带尺寸修正的电阻。尺寸修正允许用户以模型几何方式定义电阻率。在这个项目中,钛氮化物的尺寸修正特性也被用于钛铝合金。

图1:FinFET器件的3D模型,使用切割平面(中间和最右边)进行电阻测量

结果:

我们首先观察了与栅极CD相关的电阻变化,包括有和没有大小修正。结果如图2所示。

图2:金属栅电阻与栅线宽度的关系

接下来,我们按照每5纳米的增量测量了与金属栅凹槽深度相关的电阻。结果表明,在45纳米以下的W蚀刻退深度时,由于使用了SAC氮化物盖层CMP抛光步骤,电阻没有变化。

图5:60nm、50nm和35nm的刻蚀深度(从左到右)。这些图像是在SAC氮化硅帽CMP步骤之后拍摄的。

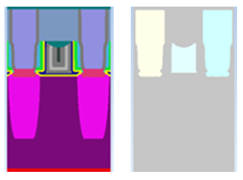

一旦我们回顾了不同的栅极电容和蚀刻深度,我们就开始关注变化的蚀刻背面轮廓。除了标准轮廓之外,还有两种可能的轮廓,分别是天线形状和尖头形状。天线形状模仿了一个量筒中的水的轮廓。在这种形状配置下,栅极的中心比边缘的钛铝和钛氮化物更深。这可能导致与名义(一致的刻蚀深度)轮廓相比更高的电阻。尖头轮廓可以想象成一支钢笔,中间保留了更多的 W,而边缘的 TiN 和 TiAl 被刻得更深。这种配置可能导致总体电阻较低。我们使用刻蚀后退步骤的图案依赖性来建模这两个轮廓。

图6(从左到右):使用模式依赖性的不同配置文件,用于天线和尖头形状。a)带有POR流的天线形状(b)具有26纳米门CD的天线配置文件(c)具有28纳米门CD的尖头配置文件(d)具有刻蚀的尖头配置文件。

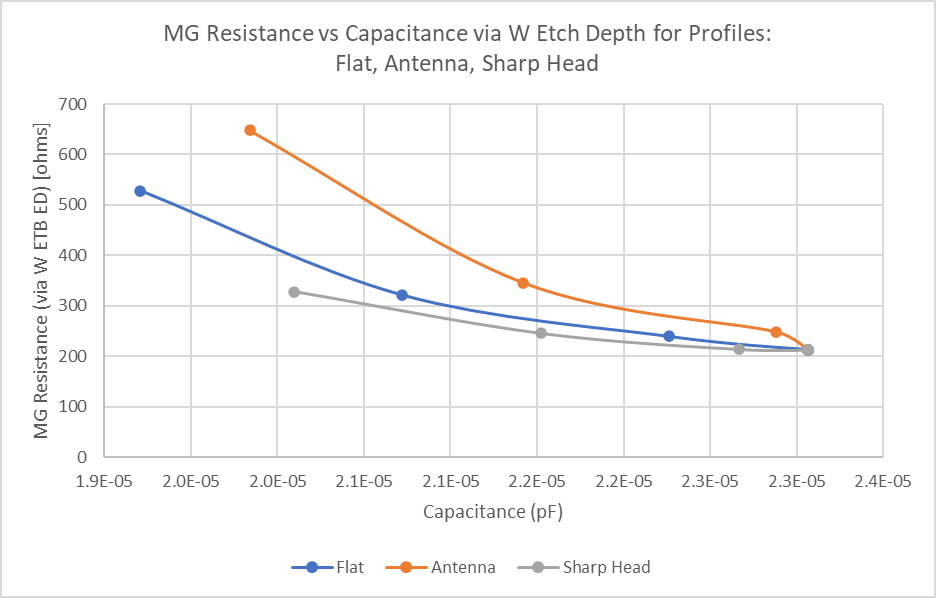

在下面显示的图表中(图7),蓝线显示了原始门CD曲线的电阻结果(我们的原始记录过程(POR)形状),而橙线显示了天线曲线的结果,灰线代表了尖头曲线。从图7可以看出,对于3种不同的曲线,电阻测量在门CD的变化上几乎相同。然而,当 W 蚀刻深度大于50nm时,抵抗测量图与 W 蚀刻深度的关系呈现出差异。抵抗值从高到低依次是天线、平坦和尖头轮廓。

图7:金属栅电阻与栅CD(左)和金属栅电阻与W刻蚀深度(右)的关系,有三个配置文件:平坦(蓝色),天线(橙色)和尖头(灰色)。

在这项研究的最后一步中,为了完成我们的电容测量,我们首先在我们的设备内建立网络。为此,我们创建了PFET和金属栅网络(参见图8)。然后,我们提取网络的电阻和电容值。与栅CD和W刻蚀深度相关的电阻和电容测量结果如图9和10所示。

图8:PFET切割示意图,显示了用于电容计算的PFET到金属接触和金属栅网。

图9:金属栅电阻与栅极CD相对于电容的关系,分别对应三种不同的金属栅配置文件:平面(蓝色),天线(橙色)和尖头(灰色)

图9:金属栅电阻与栅极CD相对于电容的关系,分别对应三种不同的金属栅配置文件:平面(蓝色),天线(橙色)和尖头(灰色)

图 10:金属栅电阻与刻蚀深度相对应的电容,针对三种不同的金属栅配置进行比较:平坦(蓝色),天线(橙色)和尖头(灰色)

图 10:金属栅电阻与刻蚀深度相对应的电容,针对三种不同的金属栅配置进行比较:平坦(蓝色),天线(橙色)和尖头(灰色)

我们的结果表明,在观察与栅极尺寸相关的电阻时,3个不同剖面的 R 和 C 值几乎没有差异。然而,当我们观察与刻蚀深度相关的电阻和电容时,我们发现锐头凹陷剖面的电容与其他剖面相似,但电阻更低。

总结:

在这项研究中,我们使用了SEMulator3D®的电气分析、模式依赖性和加速器模块来计算和更好地理解金属栅凹槽剖面对电阻和电容的影响。我们能够证明优化金属栅凹槽宽度的剖面可以改善FinFET设计中的电阻和性能。