解决方案

SOLUTION

时间: 2023-09-21

浏览量: 1024

介绍:

随着动态随机存取存储器(DRAM)单元尺寸的减小,DRAM工艺开发变得越来越困难。由于位线(BL)寻址边际和刷新时间随着单元尺寸的减小而出现问题,因为位线寄生电容(Cb)增加了。影响 Cb 的主要因素是位线与节点接触之间的寄生电容 (CBL-NC) [1]。为了减小 CBL-NC,低介电常数间隔层和气隙间隔层被提出作为可选结构用于 DRAM 存储单元架构中。

基于硅的实验可以用来评估这些低 k 值和空气隔离结构的新工艺集成方案,但在实践中这可能是耗时且昂贵的。在这项工作中,我们将展示如何使用虚拟制造来评估新的工艺集成方案,以降低 DRAM 位线的寄生电容[2]。我们将回顾一项使用氮化物-氧化物-氮化物(NON)间隔层的CBL-NC模拟研究,并评估使用低k间隔层或气隙间隔层的改进效果。此分析的目的是获得各种集成方案(NON/低k/气隙间隔层集成方案)之间的定量比较,并为工艺开发人员提供明确的指导。

流程和虚拟计量描述:

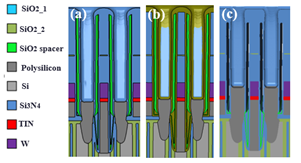

虚拟结构是使用SEMulator3D®虚拟制造平台构建的。图1显示了使用非氮间隔层(a)、低介电常数间隔层(b)和气隙间隔层(c)的最终结构。非氮间隔层由氮化物-氧化物-氮化物结构组成。低介电常数间隔层将氮化物(SN)替换为低介电常数,形成低介电常数-氧化物-低介电常数间隔层结构。气隙间隔层是通过蚀刻一个虚拟的氧化物(OX)间隔层来形成一个氮化物-气体-氮化物的间隔结构。在构建虚拟结构之后,进行了电容提取以评估使用不同工艺集成方案的CBL-NC性能。

图1:(a) 非 (b) 低 k 和 (c) 空气间隔器

图2:CBL_NC在不同的集成方案中

结果:

图2显示了使用我们选择的集成方案得出的电容结果。与原始的非比特线间距相比,低介电常数的比特线间距集成方案将 C BL_NC 提高了约16%。与原始的非间距配置相比,气隙间距集成方案将 C BL_NC 提高了约33%。

结论:

在这项研究中,使用虚拟制造技术评估了不同的工艺整合方案,以减少先进DRAM结构中的位线寄生电容。虚拟评估提供了明确而量化的指导,帮助开发人员选择能够改善先进DRAM结构中寄生电容的整合方案。