解决方案

SOLUTION

时间: 2023-09-21

浏览量: 1099

在我从事半导体设备的职业生涯开始时,晶片背面是一个让人焦虑的问题。在我职业生涯早期的一次难忘经历中,几个晶片在转移过程中飞出了机器人刀片。清理完混乱后,我们想起来可以在晶片背面沉积各种薄膜,以降低其摩擦系数。减缓晶圆传输有助于控制这个问题,但我们却给业务经理带来了困扰,他们不得不向客户解释由此导致的吞吐量减少。

尽管在晶圆背面的引入过程中遇到了困难,但当 Xilinx Virtex-7 系列的 FPGA 在 2010 年代初发布时,我开始更加关注晶圆背面。Xilinx 的产品是最早采用“堆叠硅互连技术”进行异构集成的 FPGA 之一 。这项技术使用了硅中介层,用于在不同的 FPGA 组件之间进行电信号或电力的路由传输。插层是通过在硅晶片上部分地创建穿透硅通孔(TSVs)并在顶部创建信号重分布层而形成的。硅晶片的背面经过处理以连接TSV的两端:晶片的前面临时连接到一个载体晶片上,然后将硅插层倒置处理。背面研磨和蚀刻然后被用来暴露出TSV。到赛灵思公司产品发布的时候,我已经离开了这个行业回到研究生院。TSV的金属化是课堂上的一个热门话题,由于异质集成的新发展,晶片背面成为工程师们更感兴趣的话题。

图1. 硅中间层加工。通过电穿孔和初始金属化后,晶圆的背面被磨薄以到达电穿孔位置。

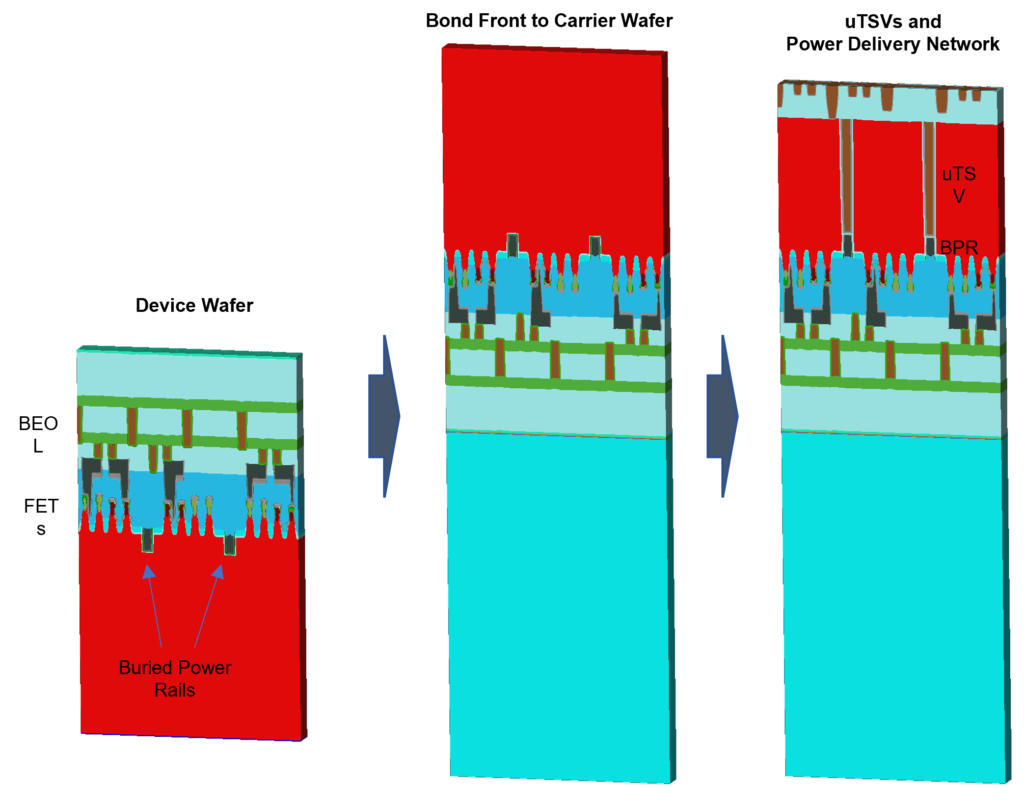

在 Xilinx FPGA 中,使用了硅中介层来处理信号和带宽需求,但更具前瞻性的方法是去除中介层,直接使用晶圆的背面进行电路布线。一个“背面”架构的例子是背面供电,即将电源从晶圆正面的传统后端制程迁移到背面。这种架构有潜力减少电源线和有源器件之间的电压下降。作为背面架构的一个例子,imec正在追求在fin级别使用埋藏式电源线。在imec的工艺流程中,导轨是在翼片之间建造的,并且类似于DRAM的埋藏字线。BEOL用于信号传输,在完成后,在器件晶圆的背面创建TSV以提供对埋藏导轨的访问。还可以在背面添加进一步的互连以供电输送。

图2. 使用埋入式电源轨道进行背面电源传递,基于[2](非按比例)

设备晶片背面的房地产对于性能来说确实很有前景。将电源线从前面移至背面将使电池缩放成为可能,并通过减少晶片前面的拥堵来限制电阻下降。领先的半导体逻辑公司非常清楚背面供电的好处,并积极致力于开发背面分配网络。英特尔在2021年中旬宣布他们将使用他们的“PowerVia”技术来实现背面供电,而台积电也讨论过在他们的下一代技术中使用埋藏式电源线。我们期待着看到晶圆背面的下一步发展。